### **1. General Description**

SL42764 is a monolithic integrated low dropout voltage regulator, with load current as high as 400mA. With the ranges for input voltage of 5V-42V, it can provide output voltage with accuracy ranges of  $\pm 2\%$ . The device is designed for application schemes for automobiles in severe environments. It is equipped with the overload, short circuit protection and overheating protection functions.

SL42764 is also applicable to all the other application schemes in need of a stable voltage during 2.5V to 20V.

With extremely low quiescent current, SL42764 is specially designed for applications in VBAT for a long term. In addition, when the cut-off of the device enables the input pin, the cut-off current is smaller than  $10\mu$ A.

## 2. Characteristics

- Shutdown currents less than 10uA

- The output voltage is adjustable, with accuracy ranges of  $\pm 2\%$ .

- The output current is as high as 400mA.

- Very broad input voltage ranges: 5~42V

- Very low dropout voltage

- Output current limiting

- Overheating cut-off protection

- Reverse polarity protection

- temperature ranges: -40°C-125°C

- ROHS

TO252-5

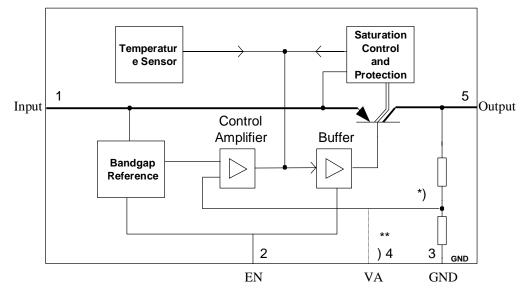

## 3. Module block diagram and pin configuration

\*) For fixed Voltage Regulator only

\*\*) For adjustable Voltage Regulator only

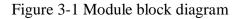

Figure 3-2 Pin configuration TO252-5 (top view)

| No. of<br>pin      | Symbol | Function                                                                               |

|--------------------|--------|----------------------------------------------------------------------------------------|

| 1                  | Ι      | <b>Input:</b> make the ceramic capacitor get close to IC for direct grounding          |

| 2                  | EN     | Enabling end: highly efficient                                                         |

| 3                  | GND    | <b>Ground:</b> Connect to the cooling fin in the device                                |

|                    | n.c.   | n.c.: no connection: an open circuit or grounding;                                     |

| 4                  | VA     | VA: voltage regulation input end: connect to an external                               |

|                    |        | voltage driver, to configure the output voltage                                        |

| 5                  | 0      | Output: connect to the foot margin through a capacitor                                 |

| 5                  | Q      | Take the capacitor value and ESR specified in the "scope of work"                      |

| Cooling foundation |        | Connect to the chip internally; connect to PCB ground and the cooling block externally |

### Table 3.1- Pin definition and functions

## 4. Electrical parameters

### **Table 4.1 Absolute Maximum Ratings**

Tj=-40°Cto 150°C. All the voltage values are relative to ground unless otherwise specified.

| Parameters                     | Symbols Limiting value |         |      | Units | Remark                |  |

|--------------------------------|------------------------|---------|------|-------|-----------------------|--|

|                                | Symbols                | Min Max |      |       | Actual K              |  |

| Input Voltage                  | VI                     | -42     | 42   | V     |                       |  |

| Enabling<br>voltage            | VEN                    | -42     | 42   | V     |                       |  |

| Temperature                    | Tj                     | -40     | 150  | °C    | Junction temperature  |  |

|                                | Tstg                   | -40     | 150  | °C    | Storage temperature   |  |

| Thermal resistance             | Rthj-a                 | 50      | 90   | K/W   | Only pin              |  |

| ESD<br>withstanding<br>voltage | VESD-HBM               | -2000   | 2000 | V     | Human body<br>mode    |  |

|                                | VESD-CDM               | -1000   | 1000 | V     | Charging device model |  |

1) The ESD withstanding voltage human body model is designed according to JESD22-A114.

2) The ESD withstanding voltage equipment model is designed according to JESD22-C101E.Notes: 1) Using by exceeding the conditions mentioned above may lead to permanent damages to the device. Long-term working at the maximum rated

Table 4.2 Scope of work

| Parameters                                       | Symbols  | Limiting | value | Unit | Note |

|--------------------------------------------------|----------|----------|-------|------|------|

|                                                  | Symbols  | Min      | Max   | Omt  | TUTE |

| Input Voltage                                    | VI       | 5        | 42    | V    | -    |

| Output<br>Capacitance<br>Require to be<br>stable | CQ       | 22       | -     | uF   | -    |

|                                                  | ESR (CQ) | -        | 3     | Ω    | -    |

| Junction<br>Temperature                          | Tj       | -40      | 150   | °C   | -    |

1) The capacitor tolerance of the minimum output capacitor shall be less than 30%

2) The maximum testing frequency of the ESR value is f=10kHz

**Notes:** Within the scope of functions or operating, IC working is described as the description of the circuit. Please refer to the Table of electrical characteristics for description of the characteristics of electrical conditions.

Table 4.3 Thermal Resistance

| Parameters | Symbols | Limiting value |                  |              | Unit | Conditions |

|------------|---------|----------------|------------------|--------------|------|------------|

|            | Symbols | Min<br>value   | Typical<br>value | Max<br>value | Cint |            |

### SL42764(TO252-5)

| Junction-to-<br>Case<br>Thermal<br>Resistance | RthJC | 3.6 | K/W | Measurement of<br>the cooling<br>foundation |

|-----------------------------------------------|-------|-----|-----|---------------------------------------------|

| Connecting                                    |       | 27  | K/W |                                             |

| of the                                        | RthJA | 115 | K/W | Only pin                                    |

| environment                                   | RtnjA | 52  | K/W | Cooling fin of 300mm2                       |

| thermal resistance                            |       | 40  | K/W | Cooling fin of<br>600 mm2                   |

1) It does not refer to production testing, but specially refers to design

### Table 4.4Appliance property

|                                          | v1 = 13.3 \ | 1              | $\leq$ Tj $\leq$ 150°C |              | Junerwise s | pecified.                                                               |

|------------------------------------------|-------------|----------------|------------------------|--------------|-------------|-------------------------------------------------------------------------|

| Parameters                               | Symbols     | Limiting value |                        |              | Unit        | Testing                                                                 |

|                                          |             | Min<br>value   | Typical<br>value       | Max<br>value | Cint        | conditions                                                              |

|                                          |             |                | Outpu                  | t Q          |             |                                                                         |

| Output<br>voltage                        | VQ          | 4.9            | 5.0                    | 5.1          | v           | SL42764<br>5mA <iq<200ma;<br>6V<vi<28v< td=""></vi<28v<></iq<200ma;<br> |

| Output<br>voltage<br>accuracy            | VQ          | -2             | -                      | 2            | %           | SL42764<br>5mA <iq<200ma;<br>5V<vi<40v< td=""></vi<40v<></iq<200ma;<br> |

| Output<br>voltage<br>adjustable<br>range | VQ.range    | 2.5            |                        | 20           | v           | SL42764                                                                 |

| Voltage<br>difference                    | Vdr         |                | 200                    | 500          | mV          | SL42764<br>IQ = 250mA<br>Vdr=VI-VQ <sup>1</sup> >                       |

| Load<br>regulation<br>ratio              | ΔVQLO       |                | 60                     | 100          | mV          | IQ=5mA to<br>400mA VI=6V<br>SL42764<br>VI=4.5V                          |

| Linear<br>adjustment<br>rate             | ΔVQLi       |                | 15                     | 40           | mV          | 12V <vi<32v;<br>IQ = 5mA</vi<32v;<br>                                   |

| Power supply rejection ratio             | PSRR        |                | 54                     |              | dB          | Fr = 100HZ<br>Vr = 0.5Vpp                                               |

| TCR                                      | dVQ<br>dT   |                | 0.5                    |              | mV/K        | 2)                                                                      |

|                                          |             | ·              | Quiescent              | current      | - <b>,</b>  |                                                                         |

| Cut-off<br>current                       | IQ          |                | 10                     | 15           | uA          | VEN=0V<br>Tj≤100°C                                                      |

| Quiescent<br>current                     | IQ          |                | 100                    | 120          | uA          | IQ=1mA;VEN=5V                                                           |

| Quiescent<br>current                     | IQ          |                |                        | 500          | uA          | IQ=400mA;<br>VEN=5V                                                     |

VI = 13.5V:  $-40^{\circ}C < Ti < 150^{\circ}C$ , unless otherwise specified

- 1) Measurement is conducted with the output voltage VQ1 when VI = 13.5 V and VI-VQ when VQ=VQ1-100mV;

- 2) It does not refer to production testing, but specially refers to design

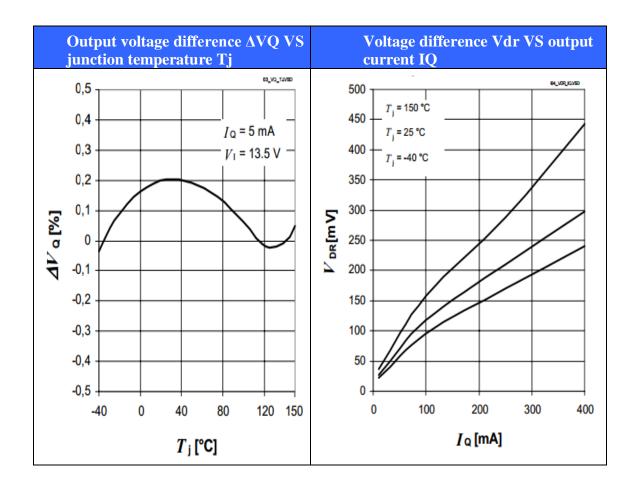

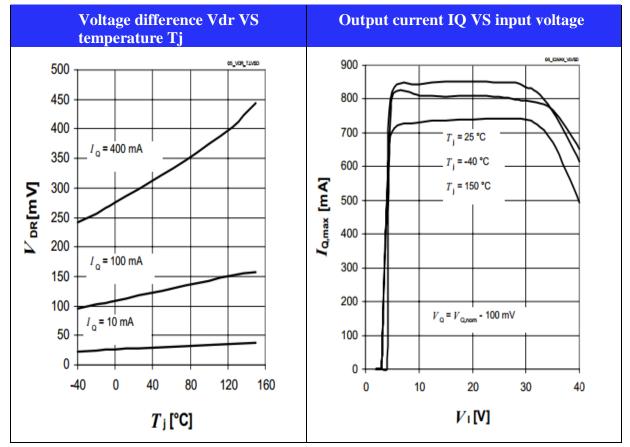

## 5. Performance characteristics of the typical voltage regulator

# SL42764

### Electrical characteristics of the enabling function

The enabling function turns on/cut off SL42764 with the EN pin. When the voltage on the EN pin is higher than VEN.H, SL42764 is turned on, in no need of pulling-up the resistance. When the voltage on the EN pin is lower than VEN.L, SL42764 is cut off.

#### Table 5.1 Electrical characteristics of the enabling end

$VI=13.5V;\ -40^{\circ}C \leq Tj \leq 150^{\circ}C$  , all the voltage values are to the ground (unless otherwise specified)

| Parameters                     | S-meh ala         | Pa           | rameters         | TT *4        | Conditions |            |

|--------------------------------|-------------------|--------------|------------------|--------------|------------|------------|

|                                | Symbols           | Min<br>value | Typical<br>value | Max<br>value | Unit       | Conditions |

| Input high<br>level            | Ven.h             | 3.5          |                  |              | V          | VQ≥4.9V    |

| Input low level                | V <sub>EN.L</sub> |              |                  | 0.5          | V          | VQ≤0.1V    |

| Internal pull-<br>down current | Ien.h             | 0.1          | 1                | 3            | uA         | VEN=5V     |

## **6.** Applications Information

**Notes:** The following information is for reference only, which shall not be regarded as certain guarantee for functions, conditions or quality.

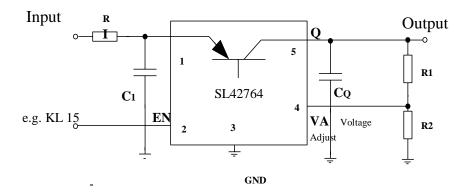

Figure 6-1 Typical application circuit

The typical application drawing of SL42764 is shown as Figure 6-1. It shows a voltage regulator with common configuration, and it is suggested to use the recommended minimum quantity of elements. Theoretically, if there is no risk of high-frequency noise, even small input filter condenser can be omitted. An output capacitor and two resistances are required for sharing the voltage when the SL42764 device is in the normal working mode. However, it depends on the environment state of the application scheme, and additional element such as an input buffer capacitor or reverse protection diode will be better.

### Input filter condenser

A small ceramic capacitor (as shown in Figure 6-1, 100nf) at the input end of the device can help filter high-frequency noise. In order to achieve the best filter result, the capacitor shall be placed closer to the input pin to the maximum extent. The input filter capacitor will not influence the stability of the regulating loop of the device.

### **Output capacitor CQ**

In any conditions, the application circuit shall be equipped with an output capacitor CQ, because as a part of the regulating loop, it can keep stable voltage. The value of the SL42764 output capacitor shall be taken by taking "Scope of work" on Page 4 as reference.

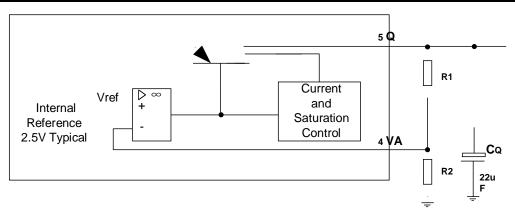

### Voltage regulator of the adjustable output voltage

The output voltage of SL42764 can be connected to the voltage adjustable pin VA through an external resistance voltage divider, to regulate between 2.5V and 20V.

The pin VA and the internal reference voltage Vref=2.5 V are connected to the error amplifier.

Figure 6-2 Logic block diagram of the VA pin of the voltage regulator

Please refer to the following formula for the output voltage (the current of VA pin is ignored)

$$VQ=[(R1+R2)/R2]*Vref$$

When:

R2<50 k $\Omega$  ignores the current flowing into the VA pin

And:

Vref: internal reference voltage 2.5V

R1: The resistance is between the adjustable output Q pin and the voltage adjustable pin VA

R2: The resistance is between the voltage regulating pin VA and the ground

When outputting the voltage of 2.5V, the voltage output pin Q shall be connected to the voltage regulating pin VA directly. Considering that the accuracy of resistance R1 and resistance R2 will increase the tolerance of the output voltage.

# 7.Package dimension profile drawing

| <u> </u>                                                                       | D                        |       |          |                  |       |

|--------------------------------------------------------------------------------|--------------------------|-------|----------|------------------|-------|

| $\leftarrow $                                                                  | $\leftarrow$ D           | SYMBO | Μ        | ILLIME           | ΓER   |

|                                                                                | $\langle \cdots \rangle$ | L     | MIN      | NOM              | MAX   |

|                                                                                |                          | A1    | 0.00     |                  | 0.10  |

|                                                                                |                          | A2    | 2.20     | 2.30             | 2.40  |

|                                                                                |                          | A3    | 1.02     | 1.07             | 1.12  |

|                                                                                | $\downarrow$             | b     | 0.55     |                  | 0.64  |

|                                                                                | E                        | b1    | 0.54     | 0.56             | 0.59  |

|                                                                                |                          | С     | 0.49     |                  | 0.56  |

| 7,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,                                        |                          | c1    | 0.48     | 0.51             | 0.52  |

| 111111111111                                                                   |                          | D     | 6.50     | 6.60             | 6.70  |

| $\bigcup \cup \cup \cup \cup \cup$                                             |                          | D1    | 5        | 5.33 RE          | F     |

| $\rightarrow \vdash_{\mathbf{b}} \stackrel{\leftarrow}{\leftarrow} \mathbf{e}$ |                          | D2    | 4        | 1.83 RE          | F     |

|                                                                                | Ă Ă                      | Е     | 9.90     | 10.1             | 10.3  |

| A                                                                              |                          | E1    | 6.00     | 6.10             | 6.20  |

|                                                                                | b PLATING                | E2    | 5.30 REF |                  | F     |

|                                                                                |                          | е     | 1.27 BSC |                  | С     |

|                                                                                | C C                      | L     | 1.40     | 1.50             | 1.60  |

|                                                                                | BAS                      | L1    | 1        | .02 RE           | F     |

|                                                                                | E SECTION A-A            | L2    | 1.70     | 1.80             | 1.90  |

|                                                                                | MET                      | θ     | 0        |                  | 8°    |

|                                                                                | AL                       | Φ     | 1.20     | )*0.1 <u>+</u> 0 | .05DP |

|                                                                                |                          |       |          |                  |       |

| $\rightarrow$ $\stackrel{\mathbf{C}}{\leftarrow}$                              |                          |       |          |                  |       |

Figure 7-1 TO252-3 Package