### 1. Overview

SL4949 is a low voltage drop LDO voltage regulator with the output voltage of 5V, integrated with the power on reset function and the input voltage monitoring function in the chip.

SL4949 can provide stable supply voltage for the control system of micro-processors, with typical output current as high as 100mA and transient input voltage of 42V, and is very suitable for applications in working environment of automotive electronics.

Supporting Reset output, it can be applied to logic control of micro-processors, in addition, it supports Sense monitoring, and can output the warning signal before the output of the reset signal. Reasonable use of the Sense monitoring function can make micro-processors conduct necessary treatment measures before the stop of micro-processors with Reset.

## 2. Characteristics

- Working voltage ranges: 5.5V~42V

- Extremely low quiescent current of 80uA in the standby ;

- High-accuracy standby output voltage: 5V±1%

- Typical output current of 100mA

- Voltage difference less than 0.4V

- It supports the Reset output function, and the reset delay time can be set;

- It supports the Sense voltage monitoring function

- Over-tempreature protection and short circuit -limiting protection

- RoHS

#### **Application fields:**

- Automobile electronics

- Personal computer

- White home appliances

- Industrial control products and electronic medical apparatus and instruments

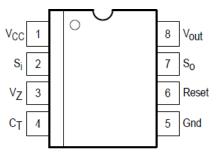

### **3.Description of pins**

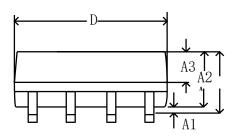

Figure 3-1 Distribution diagram of pins of SL4949

| Pin | Symbol    | Description                                         |  |  |  |

|-----|-----------|-----------------------------------------------------|--|--|--|

| 1   | Vin       | Power supply end                                    |  |  |  |

| 2   | Sense     | Voltage monitoring input end                        |  |  |  |

| 3   | Vz        | Output end of the internal pre-treatment module     |  |  |  |

| 4   | СТ        | Reset delay setting                                 |  |  |  |

| 5   | GND       | Ground                                              |  |  |  |

| 6   | Reset     | Reset output                                        |  |  |  |

| 7   | So        | Voltage monitoring output end                       |  |  |  |

| 8   | Vout      | Voltage stabilization output end                    |  |  |  |

| Ex  | posed Pad | Bottom cooling fin, with internal connection to GND |  |  |  |

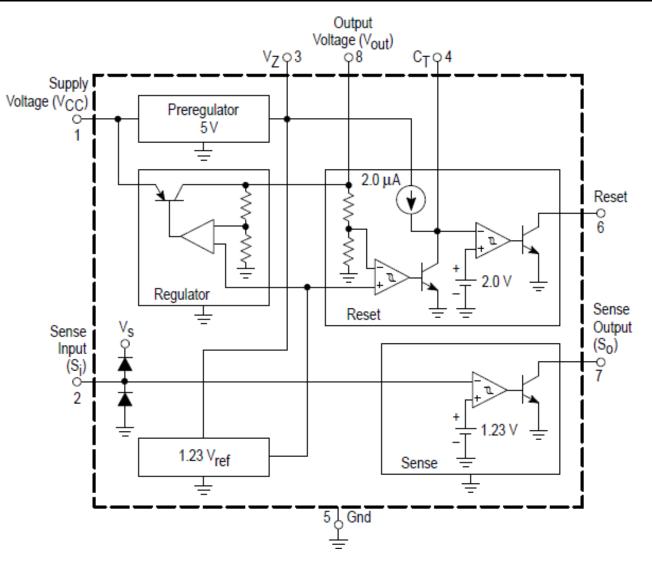

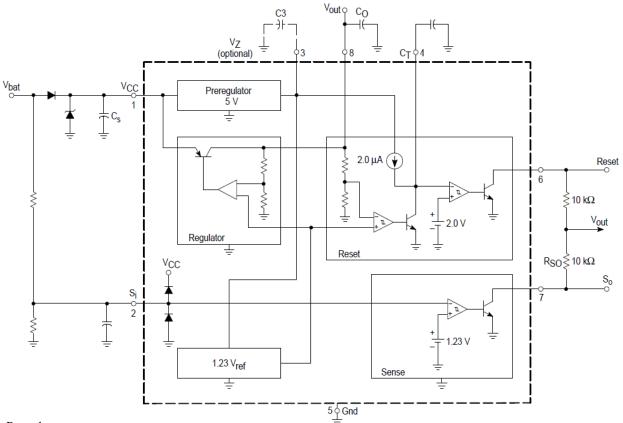

Figure 3-2 Internal schematic diagram of SL4949

## 4. Electrical parameters

| Danamatang                                                 | Symbols | Values |     |      | T 1 •4 | Duri                      |

|------------------------------------------------------------|---------|--------|-----|------|--------|---------------------------|

| Parameters                                                 | Symbols | Min    | Тур | Max  | Units  | Remark                    |

| Supply voltage                                             | Vcc     | -      | -   | 42   | V      |                           |

| Output current                                             | Iout    |        |     | 330  | mA     | Internal current limiting |

| Output voltage                                             | Vout    | 4.95   | 5   | 5.05 | V      |                           |

| Sense input current                                        | Isi     | -      | ±1  | -    | mA     |                           |

| Sense input voltage                                        | Vsi     |        | Vcc |      |        |                           |

| Output voltage of<br>the internal pre-<br>treatment module | Vz      |        | 5   |      | V      |                           |

| Output current of the<br>internal pre-<br>treatment module | Iz      |        | 5   |      | mA     |                           |

| Maximum junction temperature                               | Tj      | -      | -   | 150  | °C     |                           |

| Storage temperature                                        | Tstg    | -40    | -   | 150  | °C     |                           |

#### Table 4.1 Max. rated ranges (TA=25°C)

**Remarks:** Long-term storage of devices in environments with temperature higher than the maximum rated value will lead to influences on reliability of the devices.

The maximum rated values mentioned above are the absolute values; permanent damages will be caused

if any of the parameters exceeds the maximum value mentioned above.

| Davamatana         | Symbols       | Values |     |     | TI:4a | Domonia |

|--------------------|---------------|--------|-----|-----|-------|---------|

| Parameters         |               | Min    | Тур | Max | Units | Remark  |

| Thermal resistance | <b>R</b> thJS | -      | -   | 200 | K/W   | SL4949  |

|                    |               |        |     |     |       |         |

|                                             | ~                   | Values |          |      |       |                                                                    |

|---------------------------------------------|---------------------|--------|----------|------|-------|--------------------------------------------------------------------|

| Parameters                                  | Symbols -           | Min    | Тур      | Max  | Units | Remark                                                             |

| Output voltage                              | Vout                | 4.95   | 5.0      | 5.05 | V     | I <sub>out</sub> =1.0mA                                            |

| Output voltage                              | Vout                | 4.9    | 5.0      | 5.1  | V     | 6.0V <vcc<28v<br>1.0mA<iout<50ma< td=""></iout<50ma<></vcc<28v<br> |

| Output voltage                              | Vout                | 4.9    | 5.0      | 5.1  | V     | V <sub>CC</sub> =35V, t<1.0S<br>1.0mA <i<sub>out&lt;50mA</i<sub>   |

| Output current limiting                     | Ιουτ                | 100    | -        | 330  | mA    |                                                                    |

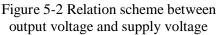

| Voltage drop                                |                     | -      | 0.1      | 0.25 | V     | Iout=10mA                                                          |

| 0 1                                         | Vdrop               | -      | 0.2      | 0.40 | V     | I <sub>out</sub> =50mA                                             |

|                                             | -                   | -      | 0.3      | 0.50 | V     | I <sub>out</sub> =100mA                                            |

| Input voltage regulation ratio              | Regline             | -      | 1.0      | 20   | mV    | 6.0V <vcc<28v<br>I<sub>out</sub>=1.0mA</vcc<28v<br>                |

| Load regulation<br>ratio                    | Regload             | -      | 8.0      | 30   | mV    | 1.0mA <iout<100ma< td=""></iout<100ma<>                            |

| Current limiting                            | ILim                | 105    | -        | 330  | mA    | V <sub>out</sub> =4.5V                                             |

| value                                       | <b>I</b> Liin       | -      | 100      | -    | mA    | V <sub>out</sub> =0V                                               |

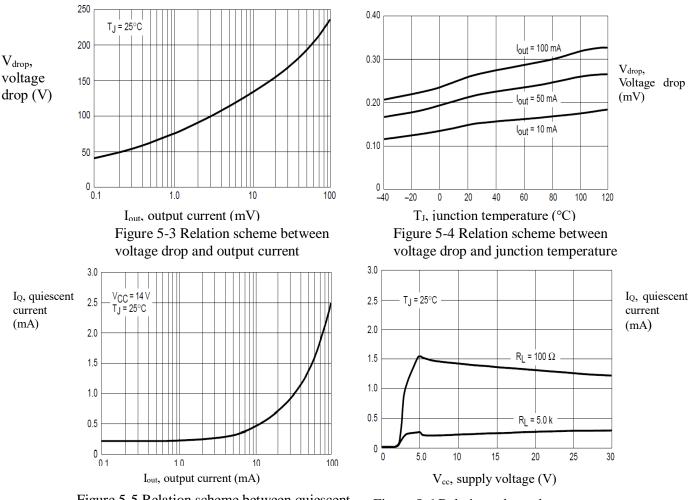

| Quiescent current                           | Iqse                | -      | 80       | 100  | uA    | I <sub>out</sub> =0.3mA,<br>T <sub>J</sub> <100°C                  |

|                                             | IQ                  |        | 350      | 400  | uA    | Iout=100mA                                                         |

|                                             |                     |        | Reset    |      |       |                                                                    |

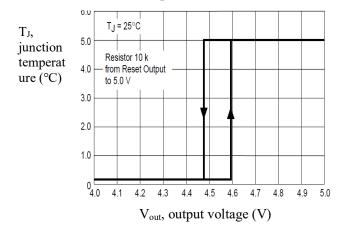

| Reset threshold voltage                     |                     |        | Vout-0.7 |      | V     |                                                                    |

| Reset threshold                             | VResth, hys         | 50     | 100      | 200  | mV    | @TJ=25°C                                                           |

| hysteresis                                  | <b>v</b> Restn, nys | 50     | -        | 300  | mV    | @TJ=-40~150°C                                                      |

| Reset delay                                 | tResD               | 55     | 100      | 180  | ms    | $\begin{array}{c} C_T = 100 nF, \\ t_R \ge 100 us \end{array}$     |

| Reset response time                         | tResR               | -      | 5.0      | 30   | us    | C <sub>T</sub> =100nF                                              |

| Reset output low level                      | tResL               | -      | -        | 0.4  | V     | R <sub>Reset</sub> =10kΩ<br>VCC≥3.0V                               |

| Reset leakage current                       | tResH               | -      | -        | 1.0  | uA    | V <sub>Reset</sub> =5.0V                                           |

| Threshold voltage<br>of delay<br>comparator | VCTth               | -      | 2.0      | -    | V     |                                                                    |

### Table 4.3 Electrical characteristics (VCC=13.5V, TA=25°C)

www.slkormicro.com

| Threshold<br>hysteresis of delay<br>comparator             | VCTth, hys      | -    | 100   | -    | mV |                                                                             |

|------------------------------------------------------------|-----------------|------|-------|------|----|-----------------------------------------------------------------------------|

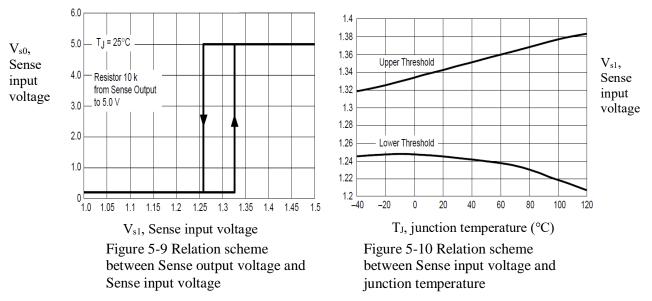

|                                                            |                 | 1    | SENSE | I    | I  |                                                                             |

| Sense threshold value                                      | VSOth           | 1.16 | 1.23  | 1.35 | V  | VSI=1.5V~1.0V                                                               |

| Sense threshold hysteresis                                 | $V_{SOth, hys}$ | 20   | 100   | 200  | mV |                                                                             |

| Sense output low<br>level                                  | VSOL            | -    | -     | 0.4  | v  | VSI $\leq$ 1.16V<br>VCC $\geq$ 3.0V<br>RSO=10k $\Omega$ to V <sub>out</sub> |

| Sense output<br>leakage current                            | Isoн            | -    | -     | 1.0  | uA | VSO=5.0V<br>VSI≥1.5V                                                        |

| Sense input current                                        | Isı             | -1.0 | 0.1   | 1.0  | uA |                                                                             |

| PREREGULATOR                                               |                 |      |       |      |    |                                                                             |

| Output voltage of<br>the internal pre-<br>treatment module | Vz              | -    | 5.0   | -    | V  | IZ=10uA                                                                     |

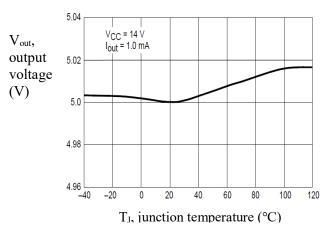

# 5. Typical parameter curve

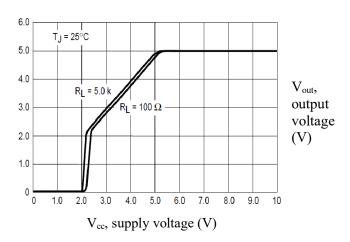

Figure 5-1 Relation scheme between output voltage and junction temperature

Figure 5-5 Relation scheme between quiescent current and output current

Figure 5-7 Relation scheme between Reset output voltage and output voltage

Figure 5-6 Relation scheme between quiescent current and input voltage

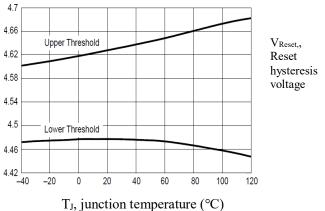

Figure 5-8 Relation scheme between Reset hysteresis voltage and junction temperature

### **6.**Applications

#### **Transient supply voltage**

Transient changes in supply voltage may lead to mis-flip of the Reset output signal. When the supply voltage is higher than 8.0V and the transient change in supply voltage is higher than 100V/us, the chip has very strong anti-jamming capability, and the Reset output signal is stable. When the supply voltage is lower than 8.0V, and the transient change of the supply voltage is lower than 0.4V/us, the Reset output signal flip will be triggered. In order to improve the anti-jamming capability of the chip when the supply voltage is lower than 8.0V, connect a capacitor to Pin 3, which (C3 $\leq$ 1.0uF) can also reduce output noises.

Remarks:

1. 1.Cs≥1.0uF, Co≥4.7uF, ESR<10Ω;

2. It is suggested to make  $C_0=C_s=10$  uF

**SL4949** is a low voltage drop LDO voltage regulator with the output voltage of 5V, which can meet requirements on power supply by micro-processor systems in automobiles, at the same time, **SL4949** is applicable to other fields. The modularized design is adopted for the chip, so that all functions can work separately.

#### 6.1 Voltage regulator

An independent vertical PNP is taken as the output device of the voltage regulator. This structure is adopted with the following advantage: When the output current achieves 100mA, the voltage drop on the output end is very small. When the input voltage is lower than 40V, the output voltage is stable, and **SL4949** will not stop working due to overvoltage pulse.

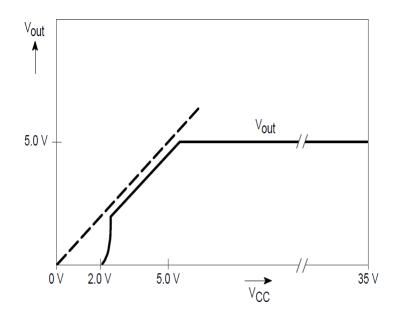

The output voltage of SL4949 changes with the change of the supply voltage, as shown in Figure 6-2.

Figure 6-2 Relation scheme between output voltage and input voltage The quiescent current of SL4949 is smaller than 100uA. When the load disconnects, with the rise in the input voltage, SL4949 keeps almost unchanged, with the typical value of 80uA.

Short circuit protection: There is a current limiting module in SL4949, with the current limiting value of 330mA.

#### 6.2 Internal preprocessing module

In order to improve the transient anti-jamming capability of the chip, there is a preprocessing module in SL4949, which provides a stable 5V internal power supply for other modules. The internal supply voltage is led out of the chip through Pin 3 (Vz). Considering of limited driving capacity of the internal supply voltage, it is suggested to not take Vz as an output end.

When the supply voltage is lower than 8V, in order to improve the transient anti-jamming capability of the chip, it is needed to add a capacitor between Pin 3 and the ground  $(100nF \sim 1.0uF)$ ; in other conditions, it is suggested to make Pin 3 suspended in midair.

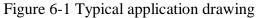

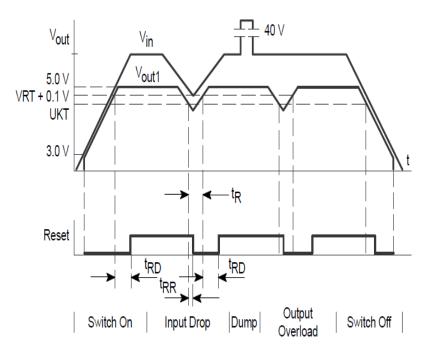

#### 6.3 Reset circuit

The schematic diagram of the Reset circuit is as shown in Figure 6-3.

Figure 6-4 Typical Reset output waveform

### 6.4 Sense comparator circuit

The Sense comparator circuit is utilized to monitor the supply voltage. The use of the external voltage divider makes the application of the Sense comparator more flexible.

Before or after the enabling of the protective diode in the chip, reasonable use the Sense monitoring input voltage to provide additional information for micro-processor of the system, such as low voltage warning.

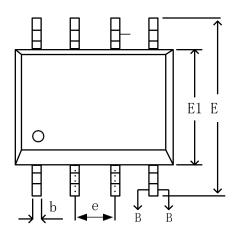

# 7.Package Specifications

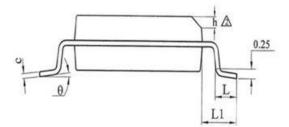

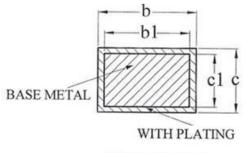

### SOP-8 package dimension

|                                   | MILLIMETER |       |        |  |  |

|-----------------------------------|------------|-------|--------|--|--|

| SYMBOL                            | MIN NOM    |       | MAX    |  |  |

| А                                 |            | -     | 1.75   |  |  |

| A1                                | 0.10       | -     | 0.225  |  |  |

| A2                                | 1.30       | 1.40  | 1.50   |  |  |

| A3                                | 0.60       | 0.65  | 0.70   |  |  |

| b                                 | 0.39       | -     | 0.48   |  |  |

| b1                                | 0.38       | 0.41  | 0.43   |  |  |

| с                                 | 0.21       | -     | 0.26   |  |  |

| c1                                | 0.19       | 0.20  | 0.21   |  |  |

| D                                 | 4.70       | 4.90  | 5.10   |  |  |

| Е                                 | 5.80       | 6.00  | 6.20   |  |  |

| E1                                | 3.70       | 3.90  | 4.10   |  |  |

| е                                 | 1.27 BSC   |       |        |  |  |

| h                                 | 0.25       | _     | 0.50   |  |  |

| L                                 | 0.50       | _     | 0.80   |  |  |

| L1                                | 1.05 BSC   |       |        |  |  |

| Ð                                 | 0          | —     | 8      |  |  |

| L/F carrier<br>dimension<br>(mil) | 80*80      | 90*90 | 95*130 |  |  |

SECTION B-B