Service hotline

+86 0755-83044319

release time:2022-04-01Author source:slkorBrowse:8383

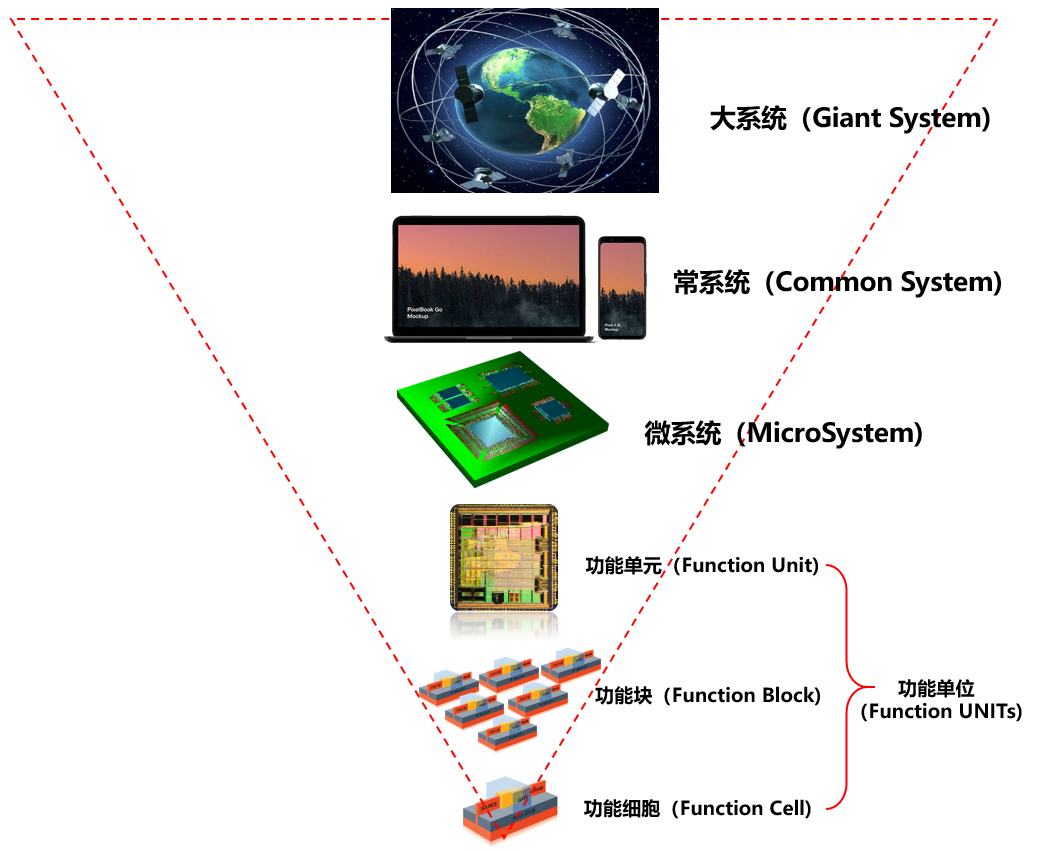

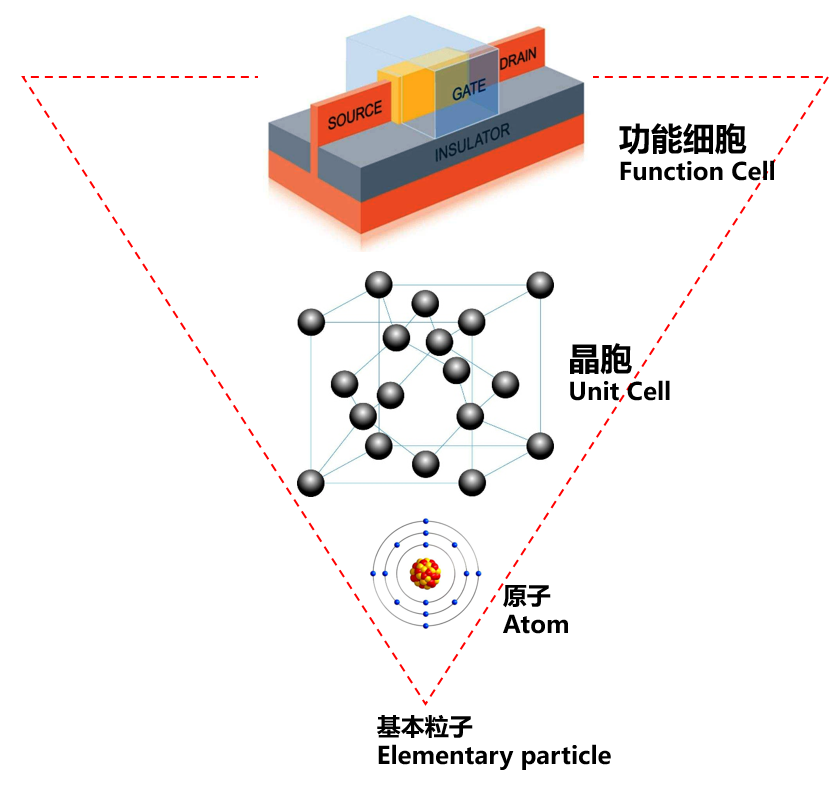

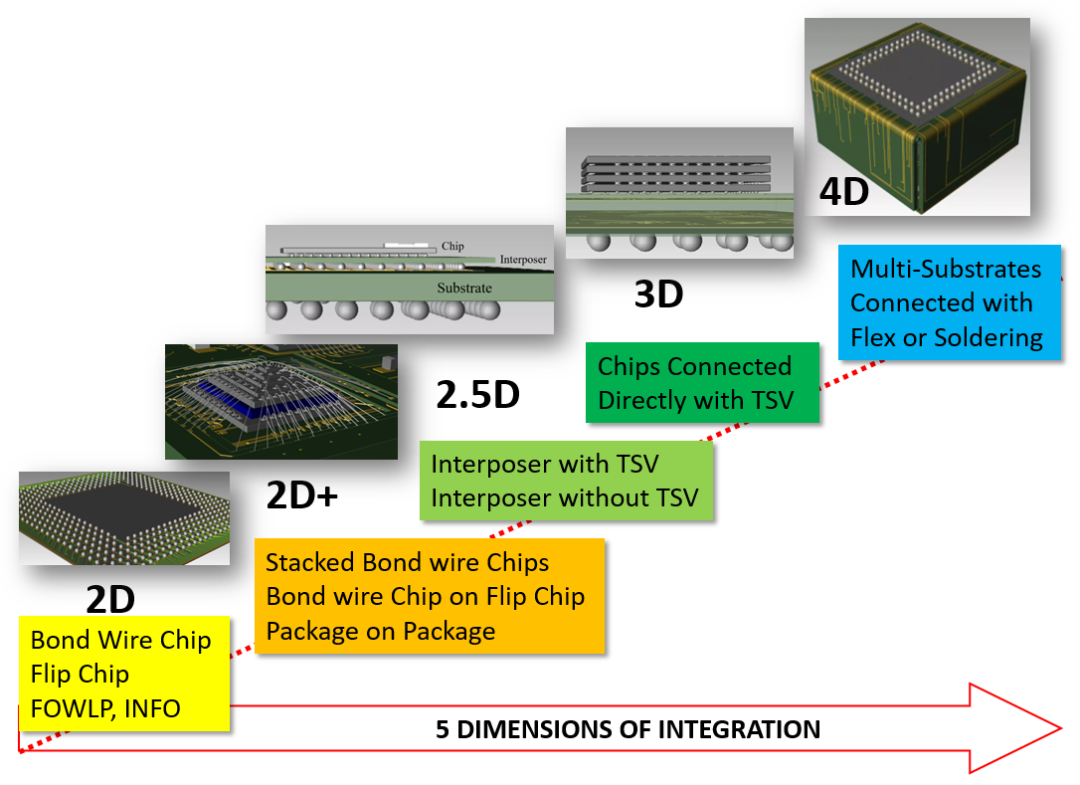

01 Scale of integration

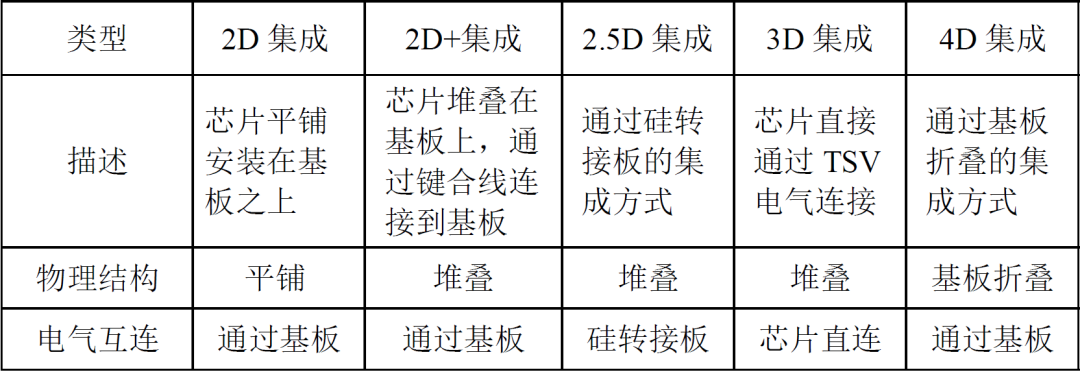

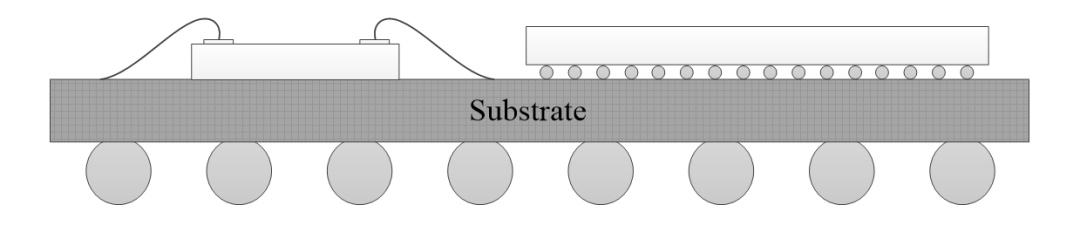

02 集成的维度

03 总结

Site Map | 萨科微 | 金航标 | Slkor | Kinghelm

RU | FR | DE | IT | ES | PT | JA | KO | AR | TR | TH | MS | VI | MG | FA | ZH-TW | HR | BG | SD| GD | SN | SM | PS | LB | KY | KU | HAW | CO | AM | UZ | TG | SU | ST | ML | KK | NY | ZU | YO | TE | TA | SO| PA| NE | MN | MI | LA | LO | KM | KN

| JW | IG | HMN | HA | EO | CEB | BS | BN | UR | HT | KA | EU | AZ | HY | YI |MK | IS | BE | CY | GA | SW | SV | AF | FA | TR | TH | MT | HU | GL | ET | NL | DA | CS | FI | EL | HI | NO | PL | RO | CA | TL | IW | LV | ID | LT | SR | SQ | SL | UK

Copyright ©2015-2025 Shenzhen Slkor Micro Semicon Co., Ltd